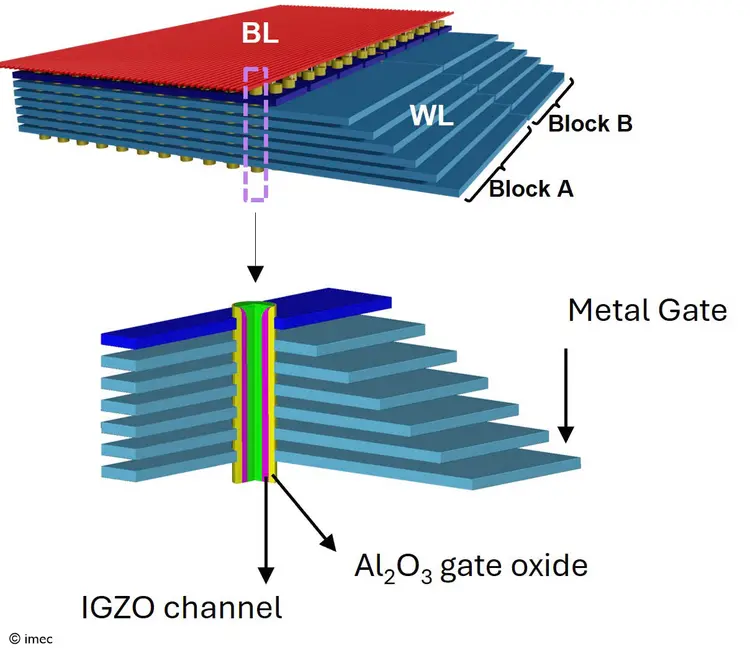

Memory operation is demonstrated on a planar proof-of-concept CCD structure which can store 142 bits. Implementing an oxide semiconductor channel material (such as IGZO) ensures sufficiently long retention time and enables 3D integration in a cost-efficient, 3D NAND-like architecture. Imec expects the 3D CCD memory density to scale far beyond the DRAM limit.

“The real value of the proposed buffer memory lies in its ability to be integrated into 3D NAND fashion, with IGZO-based CCD registers integrated into vertically aligned plugs – a concept that we now propose for the first time,” says Imec’s Maarten Rosmeulen, “from what is possible with NAND Flash today (i.e., the capability of processing 230 layers), we estimate that our 3D buffer memory can already provide five times more bit density than what (2D) DRAM is expected to offer in 2030.

We are currently investigating real 3D implementations with limited number of word lines.” The recent introduction of the CXK memory interface provides opportunities for new memories to complement DRAM in data-intensive compute applications like AI and ML. One example is the CXL type-3 buffer memory, envisioned as an off-chip pool of memories that ‘feeds’ the various processor cores with large data blocks via a high-bandwidth CXL switch.

This class of memories meets different specifications than byte-addressable DRAM, which increasingly struggles to maintain the cost-per-bit-trend scaling line. Inec proposes a CCD with IGZO c.